# A Study on Memory-Based Communications and Synchronization in Distributed-Memory Systems

Takashi MATSUMOTO <tm@is.s.u-tokyo.ac.jp>

October 15, 2001

# Department of Computer Science University of Tokyo

7-3-1 HONGO, BUNKYO-KU TOKYO, 113-0033 JAPAN

#### TITLE

A Study on Memory-Based Communications and Synchronization in Distributed-Memory Systems

#### AUTHORS

Takashi MATSUMOTO <tm@is.s.u-tokyo.ac.jp>

#### KEY WORDS AND PHRASES

memory-based communication, distributed shared memory, light-weight communication, memory-based processor, MBCF, parallel processing, PC cluster, workstation cluster

#### ABSTRACT

In terms of facilities for communications and synchronization in parallel programs, the descriptive power of the shared-memory model is equal to that of the message-passing-style (send-and-receive-type) model. From the viewpoint of performance, however, the situation is different. A very convenient way of improving performance or increasing the variety of functions is to have the communication/synchronization subsystems handle information related to the memory locations at which target data are stored. In other words, communication/synchronization subsystems based on the shared-memory model are superior to messagepassing-style subsystems which simply relay data from one task to another. This conclusion holds whether the subsystem is implemented in hardware or software. In this thesis, the Memory-Based Communications and Synchronization (MBCS) scheme is proposed. In this scheme, recognition and exploitation of information on the locations of target data by communication/synchronization subsystems is proposed, along with brand-new mechanisms based on this scheme. Three communication/synchronization mechanisms based on the MBCS scheme are then proposed. The first mechanism, called the Memory-Based Processor (MBP), is a hardware-implemented fine-grained communication/synchronization mechanism. The MBP is also a building-block for hardware-based distributed shared memory. The second is the Memory-Based Communication Facility (MBCF) which is a software-implemented medium-grained communication/synchronization mechanism made with off-the-shelf network hardware. The third is the the Memory-Based Processor II (MBP2), a hardware-implemented medium-grained mechanism which was designed and developed on the basis of research results on the MBCF. In this thesis, (1) brand-new functions to run on these mechanisms are proposed, (2) explanations of their behaviors and of high-speed implementation methods are given, (3) comparisons are made with other existing mechanisms, qualitative discussions are presented, and (4) experimental verification is described. Through these discussions, the effectiveness of the MBCS scheme will be made clear.

| REPORT DATE        | WRITTEN LANGUAGE  |

|--------------------|-------------------|

| October 15, 2001   | English           |

| TOTAL NO. OF PAGES | NO. OF REFERENCES |

| 131                | 82                |

#### ANY OTHER IDENTIFYING INFORMATION OF THIS REPORT

#### DISTRIBUTION STATEMENT

First issue 30 copies. This technical report is available via internet WEB from http://www.is.s.u-tokyo.ac.jp/tech-reports/FILES.html.

#### SUPPLEMENTARY NOTES

DEPARTMENT OF COMPUTER SCIENCE Graduate School of Information Science and Technology University of Tokyo

7-3-1 Hongo, Bunkyo-ku Tokyo, 113-0033 Japan

# A Study on Memory-Based Communications and Synchronization in Distributed-Memory Systems

# **Takashi Matsumoto**

February 2001

A Dissertation Submitted to Graduate School of Science University of Tokyo

in Partial Fulfillment of the Requirements for the Degree of Doctor of Science in Information Science

#### **Abstract**

In terms of facilities for communications and synchronization in parallel programs, the descriptive power of the shared-memory model is equal to that of the message-passing-style (send-and-receive-type) model. From the viewpoint of performance, however, the situation is different. In modern architectures for distributed-memory multicomputers, memory is an important and fundamental building-block of the nodes. It is thus directly accessed by processors that use their memory management units for protection and virtualization. Therefore, a very convenient way of improving performance or increasing the variety of functions is to have the communication/synchronization subsystems handle information related to the memory locations at which target data are stored. In more concrete terms, if communication/synchronization subsystems do so, they can use the information to reduce the number of copies of data. Moreover, these subsystems have been made capable of directly accessing data in user tasks, it becomes possible to implement advanced synchronization functions (e.g., atomic operations, queue operations and so forth), as well as simple read/write operations, within the subsystems. In short, communication/synchronization subsystems based on the shared-memory model are superior in this way to message-passing-style subsystems which simply relay data from one task to another. This conclusion holds whether the subsystem is implemented in hardware or software.

In this thesis, the Memory-Based Communications and Synchronization (MBCS) scheme is proposed. In this scheme, recognition and exploitation of information on the locations of target data by communication/synchronization subsystems is proposed, along with brand-new mechanisms based on this scheme. Effectiveness of the overall scheme is then shown by experimental verification and by discussion and analysis. Going into more detail, subsystems based on the MBCS scheme are classified into three categories that correspond to the different grain sizes of data within operations and on implementation methodology. A communication/synchronization mechanism for each category is then proposed. The first mechanism, called the Memory-Based Processor (MBP), is a hardware-implemented fine-grained communication/synchronization mechanism. The MBP is also a building-block for hardware-based distributed shared memory. The second is the Memory-Based Communication Facility (MBCF) which is a software-implemented medium-grained communication/synchronization mechanism made with off-the-shelf network hardware. The third is the the Memory-Based Processor II (MBP2), a hardware-implemented medium-grained mechanism which was designed and developed on the basis of research results on the MBCF. In this thesis, (1) brand-new functions to run on these mechanisms are proposed, (2) explanations of their behaviors and of high-speed implementation methods are given, (3) comparisons are made with other existing mechanisms, qualitative discussions are presented, and (4) experimental verification is described. Through these discussions, the effectiveness of the MBCS scheme will be made clear.

### Acknowledgments

I would like to thank professor Kei Hiraki, my boss at the University of Tokyo, for giving me the environment to conduct research on subjects of my choice. I also wish to thank Dr. Junpei Niwa and Dr. Tatsushi Inagaki (presently with IBM Japan's Tokyo Research Laboratory), who were students at our laboratory and have developed an excellent optimizing-compiler for my software DSM scheme. I also wish to thank Dr. Kiyofumi Tanaka for designing and developing the brand-new "Casablanca" embedded processor for the MBP2. He was willing to proceed with its development and to adopt my several ideas for its architecture.

I thank Mr. Shigeru Uzuhara of AXE Corp. for carrying out the laborious work of porting the *SSS–CORE* OS to run on ULTRA workstations. My thanks are also due to Mr. Haruyasu Oyobe of Sansei Systems Co. Ltd for manufacturing the logic board for the MBP2P and developing the logic design of its central controller.

I also wish to thank Ms. Noriko Tanaka, the very able secretary of our laboratory, for relieving me of most burdensome administrative tasks. I must also thank Ms. Akiko Shintani, a super-librarian in the Department of Information Science. She always helps us in our searches for literature. I am also indebted to the system administrators at our laboratory for their steady maintenance of the research environment. In particular, I wish to thank Mr. Kanemitsu Ootsu (presently with the University of Utsunomiya), Mr. Junji Tamatsukuri, Mr. Kenji Morimoto, Mr. Masayoshi Nomura and Mr. Ryuta Niino.

I would also like to thank the Information-Technology Promotion Association, Japan (IPA) for their financial support of the development of the SSS-CORE and the MBP2P. I also wish to thank Japan Science and Technology Corporation (JST) for their financial support for the development of new scheduling mechanisms in the SSS-CORE and for providing a 24-hour office for individual research. I must also thank Sun Microsystems K. K. and Inc. for providing specifications of LSIs on their workstations. These specifications were indespensable for me to develop the MBCF system and to construct the SSS-CORE OS.

I am grateful to my father, who represents my idea of the perfect scholar, and to my mother who is an ideal broad-minded Japanese mother.

# **Contents**

| 1 | Intr | roduction                                              | 1  |

|---|------|--------------------------------------------------------|----|

|   | 1.1  | Hardware DSM                                           | 1  |

|   | 1.2  | Software DSM                                           | 4  |

|   | 1.3  | Memory-Based Communications and Synchronization (MBCS) | 5  |

|   | 1.4  | Contributions                                          | 6  |

|   | 1.5  | Thesis organization                                    | 8  |

| 2 | Men  | mory-Based Processor (MBP)                             | 9  |

|   | 2.1  | Fine-grained hardware implementation of the MBCS       | 9  |

|   | 2.2  | Outline of the Memory-Based Processor                  | 9  |

|   | 2.3  | Caching in the MBP system                              | 12 |

|   | 2.4  | Address translation in the MBP system                  | 12 |

|   | 2.5  | Directory-based cache scheme in the MBP system         | 15 |

|   | 2.6  | The MBP's protocol-switching facility                  | 20 |

|   | 2.7  | 7 Related Works                                        |    |

|   |      | 2.7.1 Memory Channel (Reflective-Memory)               | 20 |

|   |      | 2.7.2 Tempest                                          | 21 |

|   |      | 2.7.3 Flash                                            | 21 |

|   |      | 2.7.4 Shrimp                                           | 21 |

| 3 | Ove  | erview of Memory-Based Communication Facility (MBCF)   | 22 |

|   | 3.1  | Middle-grained software implementation of the MBCS     | 22 |

|   | 3.2  | Background to the MBCF                                 | 22 |

|   | 3.3  | Basic concepts of the MBCF                             | 24 |

|   |      | 3.3.1 From MBP to MBCF                                 | 24 |

|   |      | 3.3.2    | Protection and security mechanisms of the MBCF                          | 25 |

|---|------|----------|-------------------------------------------------------------------------|----|

|   |      | 3.3.3    | Virtual and global addressing in the MBCF system                        | 26 |

|   | 3.4  | Illustra | ation of the MBCF's behavior                                            | 26 |

|   |      | 3.4.1    | Assumptions of network interface cards (NICs)                           | 26 |

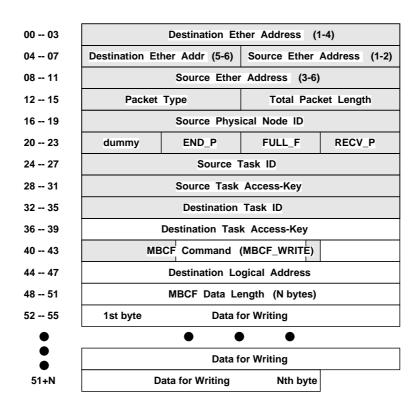

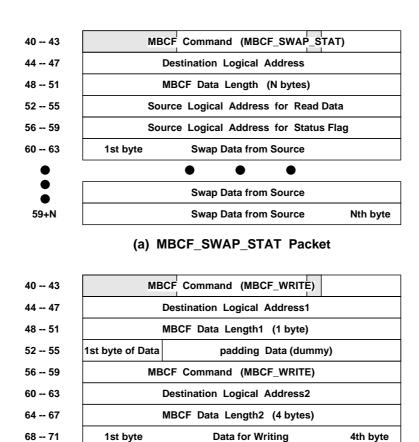

|   |      | 3.4.2    | Illustration of MBCF_WRITE operation                                    | 28 |

|   |      | 3.4.3    | Illustration of the update-cache mechanism using MBCF_WRITE             | 35 |

| 4 | Fun  | ctions o | of the MBCF                                                             | 38 |

|   | 4.1  | The co   | ommands                                                                 | 38 |

|   | 4.2  | Option   | ns for the MBCF commands                                                | 52 |

|   | 4.3  | The su   | pporting commands                                                       | 54 |

|   | 4.4  | The ru   | le for combining MBCF commands                                          | 55 |

| 5 | Disc | cussions | on the MBCF                                                             | 57 |

|   | 5.1  | High-s   | speed implementation techniques of the MBCF                             | 57 |

|   | 5.2  | A qual   | litative comparison with message-passing-style communication mechanisms | 61 |

|   | 5.3  | A qual   | litative comparison with the Active Message                             | 63 |

|   | 5.4  | Relate   | d Works                                                                 | 64 |

|   |      | 5.4.1    | Fast Message                                                            | 64 |

|   |      | 5.4.2    | Active Message                                                          | 64 |

|   |      | 5.4.3    | SparcStation Active Message                                             | 64 |

|   |      | 5.4.4    | PM                                                                      | 64 |

|   |      | 5.4.5    | U-NET                                                                   | 65 |

| 6 | An l | Implem   | entation of the MBCF using Ethernet                                     | 66 |

|   | 6.1  | Specifi  | ications of the MBCF/Ether                                              | 66 |

|   |      | 6.1.1    | Background to the MBCF/Ether                                            | 66 |

|   |      | 6.1.2    | Packet format of the MBCF/Ether                                         | 66 |

|   |      | 6.1.3    | User interfaces of the MBCF/Ether                                       | 69 |

|   |      | 6.1.4    | Protocol of the MBCF/Ether                                              | 70 |

|   | 6.2  | Evalua   | ation using SPARCstation 20s and SSS-CORE Ver.1.x                       | 72 |

|   |      | 6.2.1    | Environment used for performance evaluation                             | 72 |

|   |      | 6.2.2    | Overheads of MBCF/Ether                                                 | 73 |

|   |     | 6.2.3                             | Peak data-transfer rate of MBCF/Ether communications                                   | 77  |

|---|-----|-----------------------------------|----------------------------------------------------------------------------------------|-----|

|   |     | 6.2.4                             | Round-trip latency of the MBCF/Ether protocol                                          | 79  |

|   |     | 6.2.5                             | One-way latencies of high-level commands of the MBCF/Ether protocol                    | 82  |

|   |     | 6.2.6                             | Evaluation of performance in executing an application program                          | 83  |

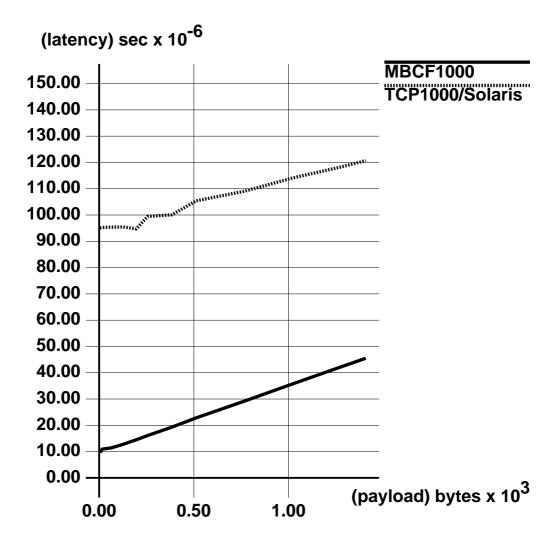

|   | 6.3 | Evalua                            | ation using ULTRA 60s and SSS-CORE Ver.2.x                                             | 88  |

|   |     | 6.3.1                             | Environment used for performance evaluation                                            | 88  |

|   |     | 6.3.2                             | Peak data-transfer rate of MBCF/Ether communications                                   | 88  |

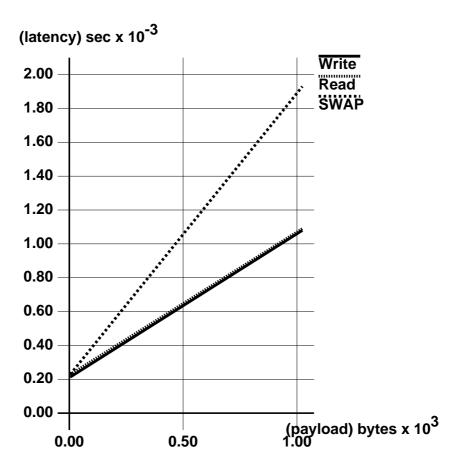

|   |     | 6.3.3                             | One-way latency of the MBCF/Ether protocol                                             | 91  |

|   |     | 6.3.4                             | One-way latencies of high-level commands for MBCF/Ether protocol                       | 91  |

|   | 6.4 | A qua                             | ntitative comparison with the user-level communication mechanisms of MPPs              | 93  |

| 7 | Con | npiler-A                          | Assisted Distributed-Shared Memory Schemes                                             | 95  |

|   | 7.1 | Softwa                            | are DSM for the medium-grained MBCS                                                    | 95  |

|   | 7.2 | Comp                              | iler-based approach                                                                    | 95  |

|   | 7.3 | My ap                             | proach                                                                                 | 96  |

|   | 7.4 | UDSM                              | If and ADSM                                                                            | 98  |

|   | 7.5 | Needs                             | of the MBCF for UDSM and ADSM $\ \ \ldots \ \ \ldots \ \ \ldots \ \ \ldots \ \ \ldots$ | 99  |

|   | 7.6 | Optim                             | ization for the UDSM and the ADSM                                                      | 99  |

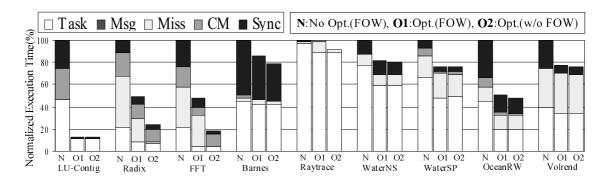

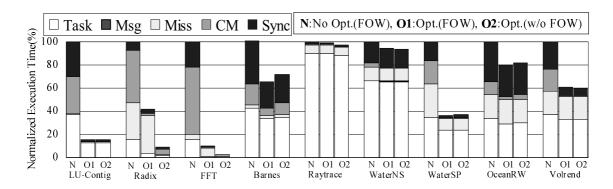

|   | 7.7 | Evalua                            | ation of my scheme and methods of optimizations                                        | 100 |

|   |     | 7.7.1                             | Evaluation environment                                                                 | 100 |

|   |     | 7.7.2                             | Performance in terms of single-node execution                                          | 102 |

|   |     | 7.7.3                             | Performance in terms of 16-node execution                                              | 103 |

|   |     | 7.7.4                             | Adding nodes for increased speed                                                       | 104 |

|   | 7.8 | Relate                            | d Works                                                                                | 104 |

|   |     | 7.8.1                             | Shasta                                                                                 | 104 |

| 8 | Men | nory-Ba                           | ased Processor II (MBP2)                                                               | 106 |

|   | 8.1 | Middle                            | e-grained hardware implementation of the MBCS                                          | 106 |

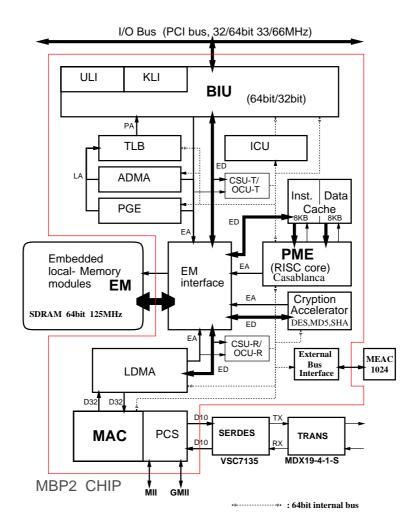

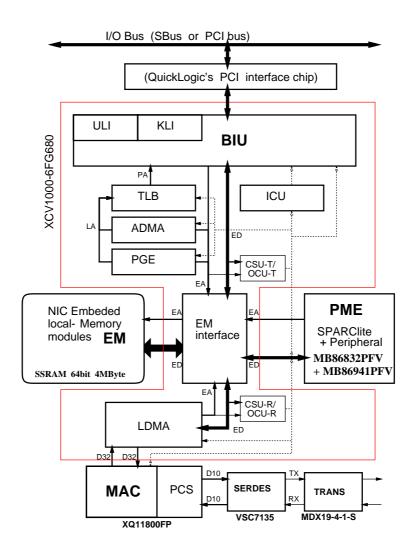

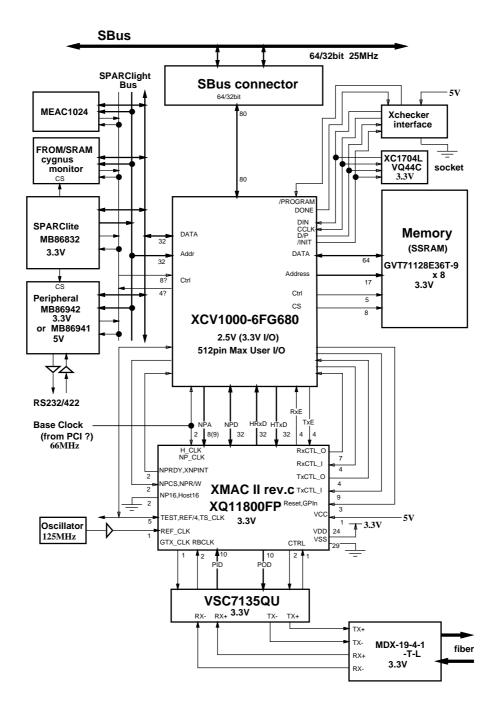

|   | 8.2 | 3.2 System structure of the MBP2C |                                                                                        | 108 |

|   | 8.3 | Featur                            | es of the MBP2                                                                         | 111 |

|   |     | 8.3.1                             | Architecture based on the MBCF                                                         | 111 |

|   |     | 8.3.2                             | Protected and virtualized user-level direct I/O access                                 | 112 |

|   |     | 8.3.3                             | Full-DMA-connection among functional units                                             | 112 |

| Embedded microprocessor with zero-cost context switching for interrupts Encryption hardware embedded in a NIC |

|---------------------------------------------------------------------------------------------------------------|

| ype of the MBP2C                                                                                              |

|                                                                                                               |

| sions on the MBP2                                                                                             |

|                                                                                                               |

| d Works                                                                                                       |

| T3D                                                                                                           |

| AP1000+                                                                                                       |

|                                                                                                               |

# **List of Tables**

| 6.1  | Sending overheads of MBCF_WRITE packets                                                    | 74  |

|------|--------------------------------------------------------------------------------------------|-----|

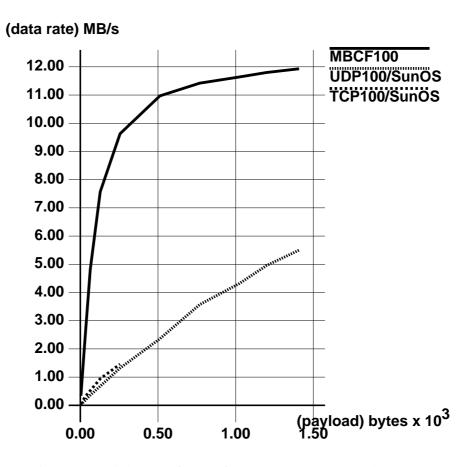

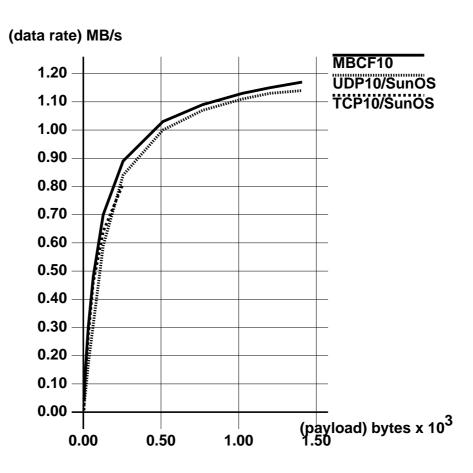

| 6.2  | Peak data-transfer rates for the MBCF/100BASE-TX and the MBCF/10BASE-T $\ \ldots \ \ldots$ | 77  |

| 6.3  | Round-trip latency of MBCF/100BASE-TX                                                      | 80  |

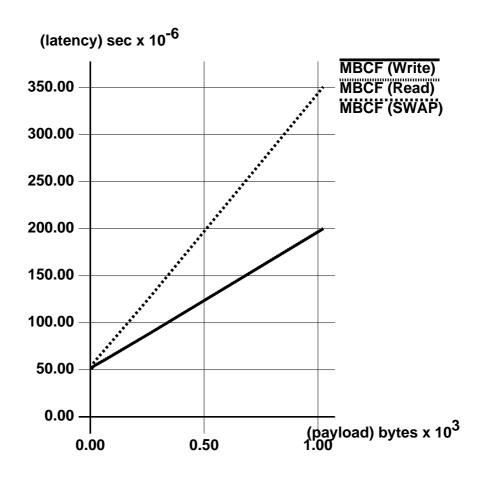

| 6.4  | One-way latencies of high-level commands of MBCF/100BASE-TX                                | 83  |

| 6.5  | Execution times of parallel ray-tracing using MBCF/100BASE-TX                              | 86  |

| 6.6  | Execution times of parallel ray-tracing using UDP100/SunOS                                 | 86  |

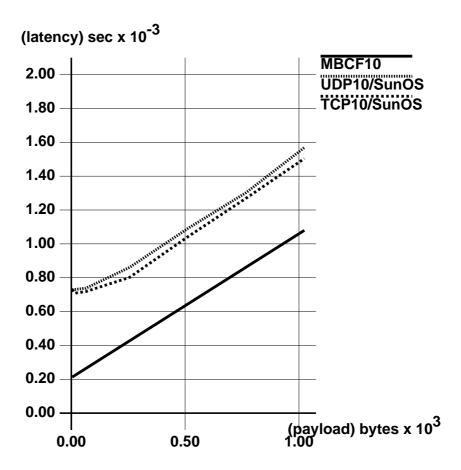

| 6.7  | Execution times of parallel ray-tracing using MBCF/10BASE-T                                | 87  |

| 6.8  | Execution times of parallel ray-tracing using UDP10/SunOS                                  | 87  |

| 6.9  | Peak data-transfer rates of MBCF/1000BASE-SX and TCP1000/Solaris                           | 89  |

| 6.10 | One-way latency ( $\mu sec$ ) of MBCF/1000BASE-SX                                          | 91  |

| 6.11 | One-way latencies ( $\mu$ sec) of high-level commands of MBCF/1000BASE-SX                  | 93  |

| 6.12 | Basic performance of user-level communication mechanisms                                   | 94  |

| 7.1  | Modifications on SPLASH-2 programs                                                         | 101 |

| 7.2  | Problem scale and single-node execution times (exec. time: sec, (additional overhead:%))   | 102 |

| 8.1  | Operational environment of the MBP2P                                                       | 115 |

| 8 2  | Hardware specifications of the MRP2P                                                       | 117 |

# **List of Figures**

| 2.1  | System architecture using MBPs                        | 10 |

|------|-------------------------------------------------------|----|

| 2.2  | Structure in one node of the MBP system               | 11 |

| 2.3  | TLBs in one node of the MBP system                    | 13 |

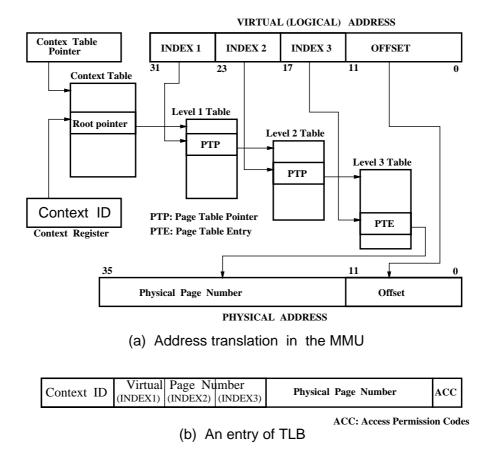

| 2.4  | Address translation in the MBP system                 | 14 |

| 2.5  | Hierarchical bitmap directory (1)                     | 16 |

| 2.6  | Hierarchical bitmap directory (2)                     | 17 |

| 2.7  | Hierarchical multicasting                             | 18 |

| 2.8  | Acknowledge-message combining                         | 19 |

| 3.1  | Functions of conventional NICs                        | 27 |

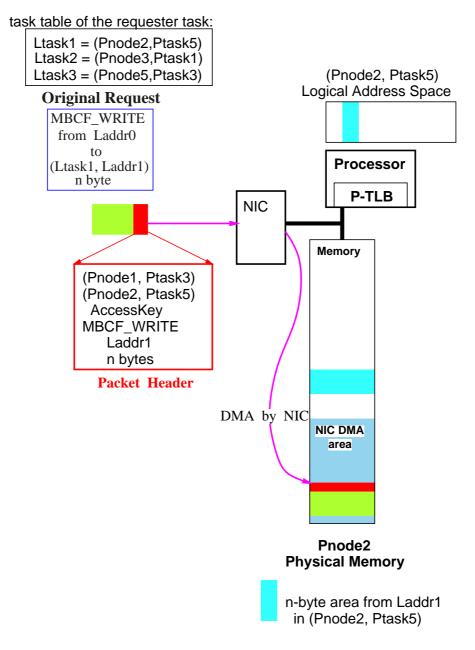

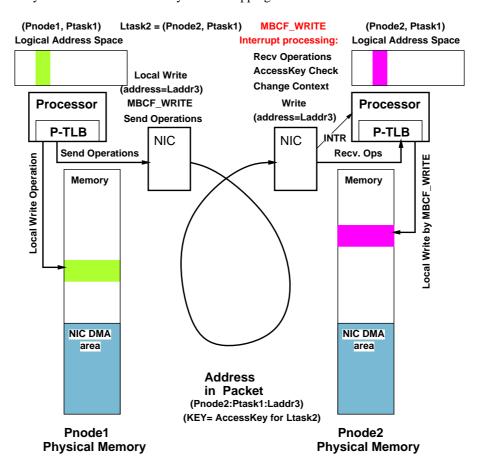

| 3.2  | Illustration of the MBCF_WRITE operation (1)          | 28 |

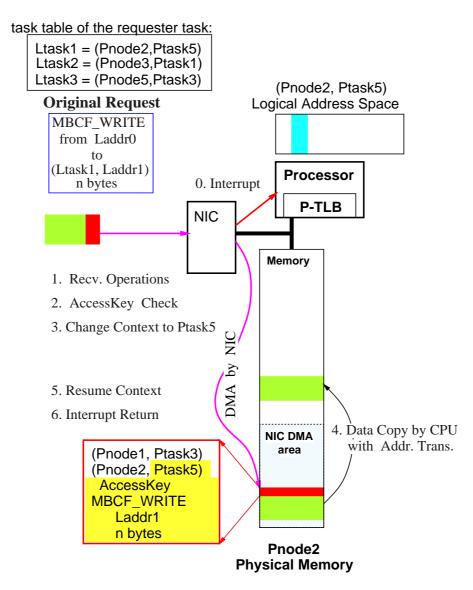

| 3.3  | Illustration of the MBCF_WRITE operation (2)          | 29 |

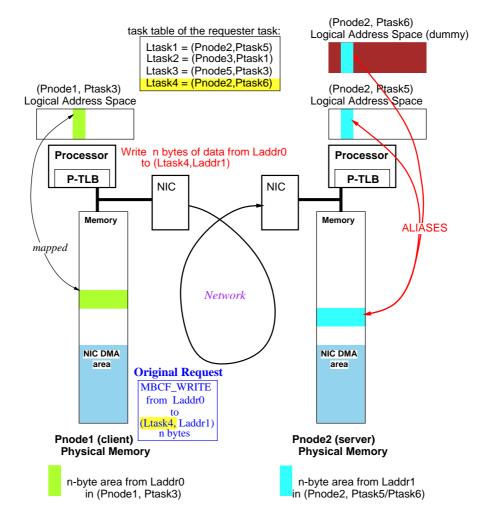

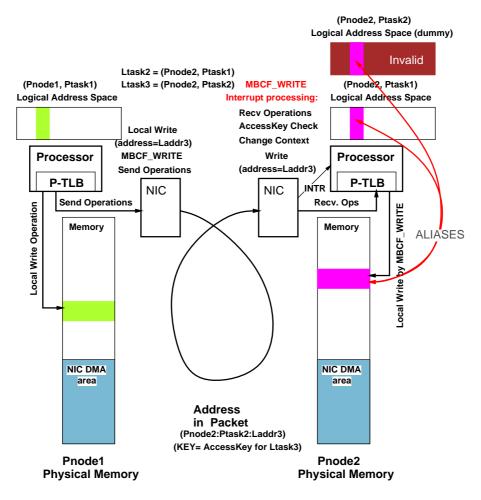

| 3.4  | Illustration of the MBCF_WRITE operation (3)          | 30 |

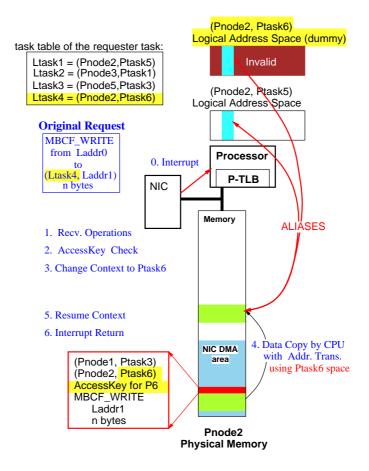

| 3.5  | Illustration of the MBCF_WRITE operation (4)          | 31 |

| 3.6  | Illustration of a secure MBCF_WRITE (1)               | 32 |

| 3.7  | Illustration of secure MBCF_WRITE (2)                 | 33 |

| 3.8  | Illustration of cache updating with MBCF_WRITE        | 34 |

| 3.9  | Illustration of cache updating with secure MBCF_WRITE | 35 |

| 3.10 | Illustration of the MBP's update process              | 36 |

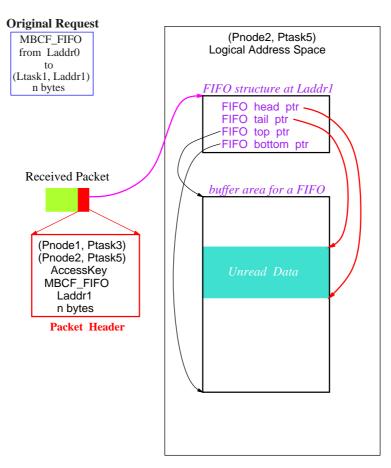

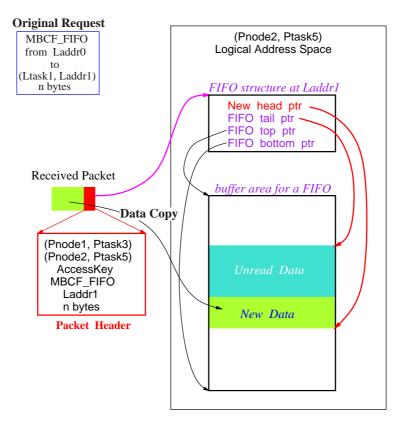

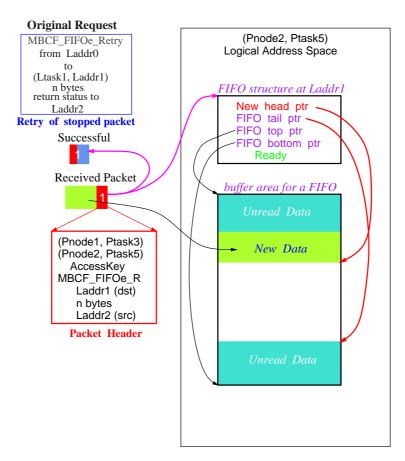

| 4.1  | Operation of the MBCF_FIFO (1) command                | 41 |

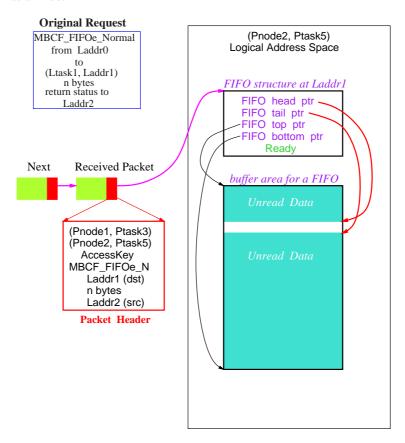

| 4.2  | Operation of the MBCF_FIFO (2) command                | 42 |

| 4.3  | Operation of the MBCF_FIFOe (1) command               | 43 |

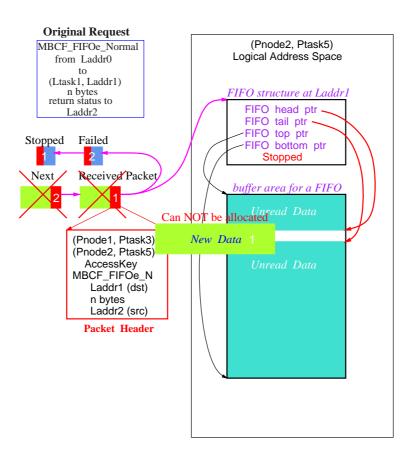

| 4.4  | Operation of the MBCF_FIFOe (2) command               | 44 |

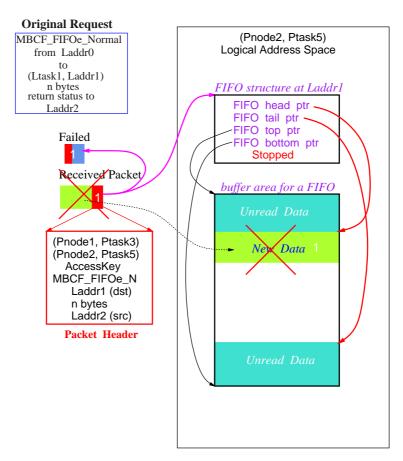

| 4.5  | Operation of the MBCF_FIFOe (3) command               | 45 |

| 4.6  | Operation of the MBCF_FIFOe (4) command                                     | 46  |

|------|-----------------------------------------------------------------------------|-----|

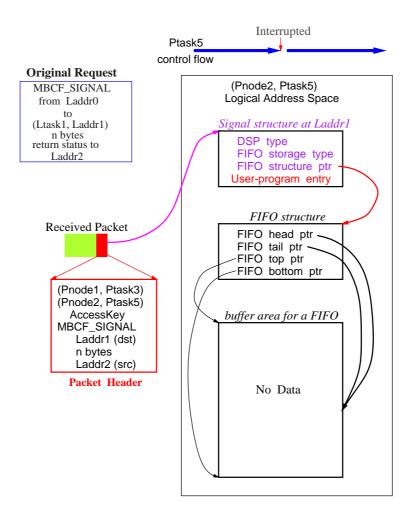

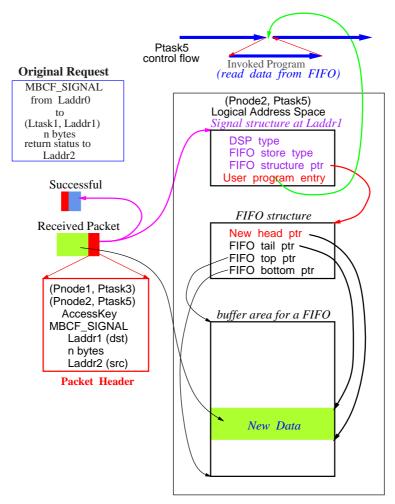

| 4.7  | Operation of the MBCF_SIGNAL (1) command                                    | 47  |

| 4.8  | Operation of the MBCF_SIGNAL (2) command                                    | 51  |

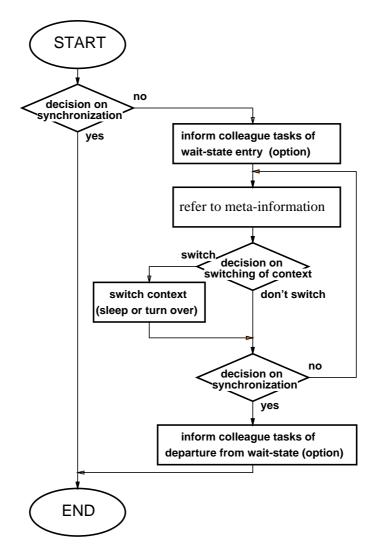

| 4.9  | Algorithm of snoopy spin-wait (SS-wait)                                     | 54  |

| 5.1  | MMU and TLB of recent processors                                            | 59  |

| 6.1  | Format of a single MBCF_WRITE packet                                        | 67  |

| 6.2  | Two other MBCF packets                                                      | 69  |

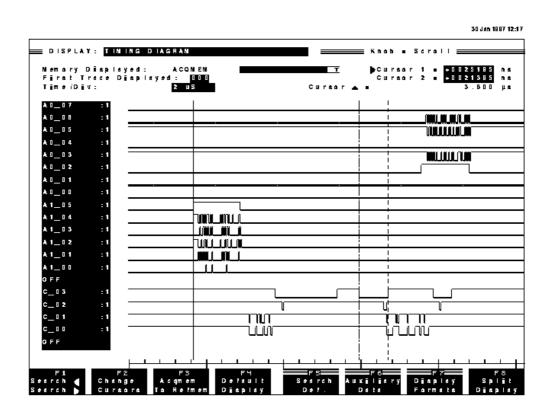

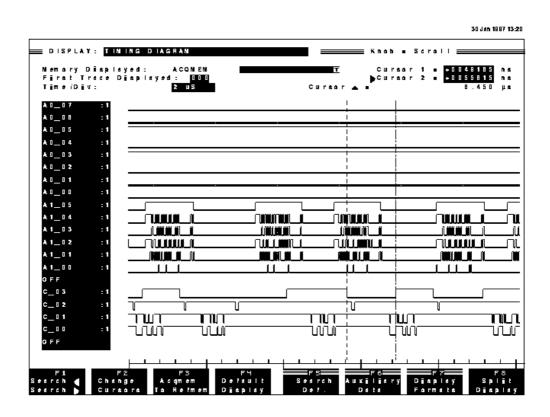

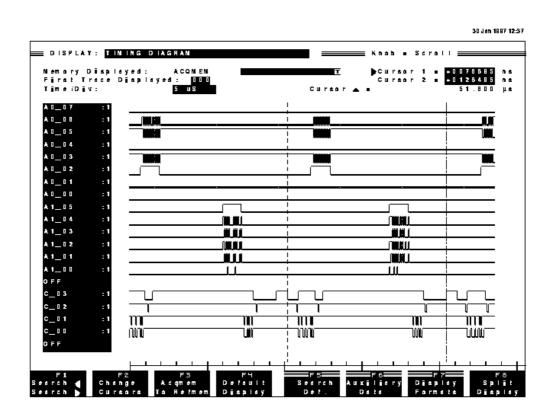

| 6.3  | Zoomed signal wave forms of a single 4byte MBCF_WRITE                       | 75  |

| 6.4  | Signal wave forms for the receiving of consecutive 4byte MBCF_WRITEs        | 76  |

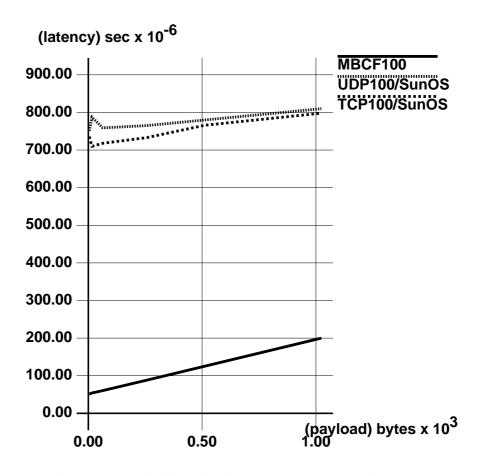

| 6.5  | Peak data-transfer rates for MBCF100, TCP100, and UDP100                    | 78  |

| 6.6  | Peak data-transfer rates for MBCF10, TCP10, and UDP10                       | 79  |

| 6.7  | Round-trip latency of MBCF/100BASE-TX                                       | 80  |

| 6.8  | Round-trip latencies for MBCF100, TCP100, and UDP100                        | 81  |

| 6.9  | Round-trip latency of MBCF/10BASE-T                                         | 82  |

| 6.10 | Round-trip latencies for MBCF10, TCP10, and UDP10                           | 83  |

| 6.11 | Signal wave forms of a single 4byte MBCF_WRITE                              | 84  |

| 6.12 | Sample picture used for measurements                                        | 85  |

| 6.13 | Peak data-transfer rates for MBCF1000 and TCP1000/Solaris using 1000BASE-SX | 89  |

| 6.14 | One-way latencies for MBCF/1000BASE-SX and TCP1000/Solaris                  | 92  |

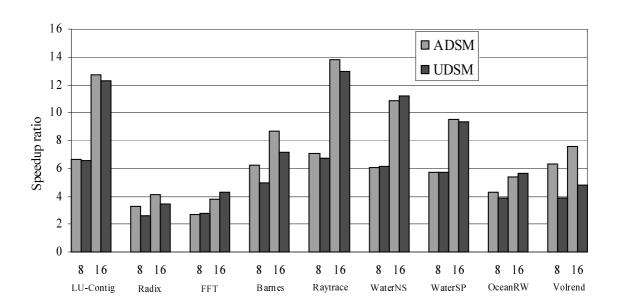

| 7.1  | Effects of UDSM optimization techniques on 16-node execution                | 103 |

| 7.2  | Effects of ADSM optimization techniques on 16-node execution                | 104 |

| 7.3  | Speed-up ratios by the UDSM and the ADSM                                    | 105 |

| 8.1  | Block diagram of MBP2C                                                      | 107 |

| 8.2  | Block diagram of the MBP2P                                                  | 115 |

| 8.3  | Circuit diagram of the NIC based on the MBP2P                               | 116 |

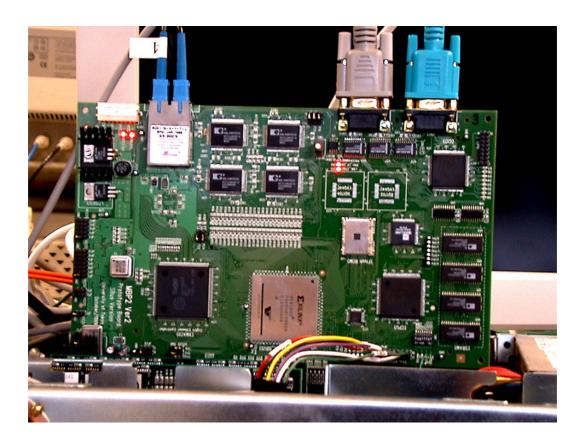

| 0 1  | Dhoto of the MDDOD NIC cord                                                 | 117 |

# Chapter 1

# Introduction

### 1.1 Hardware DSM

Recent generations of high-end microprocessors have strong and hierarchical memory systems, and cacheable memory operations are much more efficiently handled than non-cacheable operations (e.g., I/O register operations). Thus when an I/O device requires a high-bandwidth, it will includes cacheable DMA mechanism. For inter-processor communications and synchronization the situation is the same as for high-performance I/O, and memory-coupling is much better than register-coupling for communicating with many processors and I/O devices. Moreover, if we adopt a single and global memory space (i.e., shared-memory), the memory-coupling approach has further advantage in that multi-tasking operating systems on single processors can easily be ported to UMA (Uniform Memory Access)-type multiprocessors. In this way, each task can be allocated to a different processor, and this simple strategy is enough to improve the overall performance of the system.

For the above reasons tightly-coupled (UMA-type) multiprocessors, which we have recently come to call SMPs (symmetric multiprocessors), became fit for practical use in the latter half of the 1980s. This was earlier than the practical application of distributed-memory, that is, NUMA (non uniform memory access) architectures multiprocessors. It is, however, very difficult to make large-scale tightly-coupled multiprocessors because a mechanism that efficient access to main memory by multiple different processors is almost impossible. To attain a scale-up of the number of processors, the focus of research gradually shifted to distributed-memory multiprocessors. In order to obtain the benefits of shared-memory, even from distributed-memory multiprocessors, distributed-shared-memory (DSM) mechanisms became the subject of extensive study from the end of the 1980s.

Although snoop cache [15, 3] mechanisms are usually adopted for small-scale tightly-coupled multiproces-

sors, directory-based caching schemes are used in distributed-memory multiprocessors with hardware-based DSM mechanisms. This is because snoop cache mechanisms require some method for the broadcasting of memory transactions to all processors in the system to maintain consistency of the caches. Historically, the directory cache [73] was invented much earlier than the snoop cache, but early directory caches were used with UMA-type high-end multiprocessors (e.g., main frames). In such machines, all memory modules have their own directories, and the memory modules are symmetrically connected to the processor elements via switching networks. This type of directory cache is not very different to the snoop cache, and the only difference is that snoop caches exploit the merits of the bus connections between processors and main memory. At the end of the 1980s new types of directory caches [31, 1, 6] were proposed and developed for use with large-scale DSM machines. To ensure bandwidth between the processor (or a few processors) and main-memory module, new machines handle the processor(s) and memory module as a combined building block of the system. We call such a building block a **node** of the system. The overall main memory consists of memory of all memory modules in all nodes, and directories for the DSM mechanism are also distributed to all nodes. For main memory modules, every block, per cache-block size, is accompanied by a state tag and a directory which represents either nodes that are keeping copies of the block or the original (home) node of the block. When processors write to a shared block in main memory, some consistency-maintenance action is taken by the DSM mechanism. This represents a revival of directory-caching schemes. In most DSM systems, invalidate-type consistency protocols are adopted to maintain coherence because of the resulting reduction in network traffic. Hardware DSM mechanisms realized a logical shared-memory space with remote caching on multiprocessors with distributed memory, but the cost of remote access was too great to improve performance by parallel execution. In particular, invalidate-type protocols are very poor at such method of optimization as latency-hiding by overlapping phases for calculations and phases for communications. Moreover, when operating systems designed for tightly-coupled multiprocessors are ported to DSM machines without modification, it is not possible to improve performance by allowing a loss of access-locality within the node. DSM systems create a need for new operating systems that take account of the distribution of data and the distribution of tasks to minimize inter-node communications. Furthermore, a large quantity of high-speed tag-memory modules must be added to main memory so that the hardware DSM mechanisms can operate. These tag modules and the dedicated and special controller for the DSM raise the cost of DSM systems. For all of these reasons, hardware DSM systems have yet to become standard or popular.

A major by-product of research into hardware DSM was a deeper understanding of memory-consistency models. Hardware DSM mechanisms have been unable to attain negligible latencies for remote accesses, and the stalling of processors during these latencies dramatically worsens system-performance, processors were

allowed to perform the subsequent memory accesses before in-progress memory accesses had been completed. This mitigation of the memory-access rule results in a modification of the memory-consistency model, and is not possible without special conditions. Before the resulting research into memory models, processors had only been able to perform subsequent memory-access after all in-progress accesses had finished. In such a memory-access model, it is never possible for other processors to detect situations in which one in-progress access finishes while some previous accesses have not been completed. Even when a processor issues a subsequent access without waiting for all in-progress accesses to be completed, it is a good enough condition that other processors are not able to detect any inconsistencies of order. However, in DSM systems with remote caches, it is very difficult to ensure the order of memory-access operations from the viewpoint of external processors if a processor does not wait for all preceding accesses to be completed. Therefore, the memory models which had been expected by programmers were modified to mitigate their requirements. Memory operations on shared data are separated into those for data transfer and those for synchronization, and there are then no restrictions on the order of memory-access operations that correspond to data transfer. On the other hand, there are some restrictions (order-relations) between operations that are for data transfer and those that are for synchronization, or among those that are for synchronization. This is the basic idea, in outline form, of relaxed memory-access models (e.g., Release Consistency model[13], Weak Consistency model[9]). After the invention of relaxed memory models, large-scale parallel applications have gradually come to be written around these models.

Even if programmers use relaxed memory models to write shared-memory parallel programs, DSM machines were not superior to these distributed-memory machines that used message-passing-type communication mechanisms, in terms of their performance of on large-scale parallel applications. Therefore, at the start of the 1990s data-parallel computation or SPMD (single program multiple dataflow) computation on the simple distributed-memory machines then in existence became very popular in the field of scientific computation. The problems are cast in an explicitly and massively parallel form. Thoughtless researchers who saw this situations concluded that DSM machines are fundamentally inferior to simple distributed-memory multiprocessors. In fact, at the start of the 1990s, DSM multiprocessors were expensive but inefficient in the parallel execution of applications. In a sense, however, the comparison is not fair because fully-optimized code was used on the distributed-memory multiprocessors while the DSM multiprocessors of those days had, as yet, no facilities for code optimization. The biggest weak point of the DSM multiprocessors of those days was that each system has had a single and global protocol to maintain the consistency of shared memory. As I mentioned before, most such systems only included invalidate-type protocols, but invalidate-type protocols are very poor in terms of optimization for eager transmissions. Some multiprocessors had only

update-type protocols, but their performance was, in general, much worse than the performance of machines with invalidate-type protocols alone. This is because update-type protocols destroy the memory-access localities of the application program which are the source of the speed increase provided by the hierarchical memory/cache system. At the end of the 1980s I insisted that a form of dynamic protocol switching would be effective even in tightly-coupled multiprocessors [38, 40, 50], and, at the start of the 1990s I also claimed that dynamic protocol switching, according to the data-types, is much more effective in DSM multiprocessors than in tightly-coupled machines [34, 45]. If a DSM machine has multiple protocols (e.g., invalidate-type, update-type, simple remote-write without remote caching, and so forth) and a facility to switch protocols per page (memory block) or per access, the optimization techniques which had been applied to distributed-memory machines can also be applied to a DSM machine. I proposed such a hardware DSM machine, the Memory-Based Processors (MBP) [34] system in 1992. Aside from the protocol-switching facility, the MBP has various features to reduce overheads on the DSM and to lower the hardware cost of the system. The details are given in Chapter 2.

#### 1.2 Software DSM

In 1988 K. Li developed a new software solution for the generation of shared virtual spaces on clusters of PCs [32] by exploiting the memory-page management mechanisms of the processors. In recent generations, high-end microprocessors have included page-management units, and illegal access to pages which are not mapped or allowed for the allocated task (process) is detected by page-traps. K. Li exploited this mechanism to detect shared-write access to shared pages and shared-read access to invalidated pages without using any dedicated hardware. The software DSM method was thus established by this invention, and this trap-based (or OS-based) software DSM was widely accepted as a way of constructing shared-memory spaces on distributed-memory multicomputers without any hardware support for DSM.

However, K. Li's software DSM, which was called "IVY", carried large software overhead in the form of trap-handling routines. This was largely because of the larger overhead of communications in those days. There was also another problem with the IVY approach in that cache-block sizes were limited to the same size as a page or larger. This was too large to avoid false-sharing or wasteful transmissions. At the start of the 1990s, the concept of relaxed memory models was introduced to software-based DSM mechanisms, to relieve the systems of such overheads [26]. Relaxed memory models were very useful in allowing overlaps between and within communications and calculations, and thus providing improved performance.

If we adopt new relaxed-memory models, application codes may have to be rewritten and will at least have to be recompiled. In other words, the exploitation of relaxed models by software-based DSM schemes means that binary compatibility with tightly-coupled multiprocessor systems must be abandoned. Mature consideration leads us to the conclusion that binary compatibility is, in any case, useless for or irrelevant to parallel processing because of the absence of standard architectures. For this reason, I discarded the convention that trapping on load/store operations to shared pages should be exploited in software DSM schemes. In the middle of the 1990s I proposed a brand-new approach to the software-based DSM [51, 48]. In my approach, user-level codes for consistency management are inserted into the program code at compile time, and thus included in the executable files, and both the original code and the inserted codes are thoroughly optimized to reduce overheads and the need for remote communications. Details of my approach is described in Chapter 7.

### 1.3 Memory-Based Communications and Synchronization (MBCS)

From 1994, when the *SSS–CORE* project [36] started, I began to develop kernel-level software to emulate the MBP's functions. The result was the Memory-Based Communication Facility (MBCF) [46, 52, 47]. Through the development of the MBCF, I came to notice the following significant fact. The biggest advantage of a DSM scheme (or a global shared addressing scheme) is that information on the target locations is exploited in the communication/synchronization subsystem, whether the subsystem is implemented in hardware or software. Conversely, the use of logical global addresses is essential for the communication/synchronization subsystem. I call this methodology the Memory-Based Communications and Synchronization (MBCS) scheme. The MBCS scheme has following strong points comparing with conventional message-passing-style communication schemes.

- 1. The communication/synchronization subsystem can directly process the target locations and consequently reduce the number of copies of data that must be generated.

- 2. The communication/synchronization subsystem can provide users with a wide variety of functions because of the capability of specifying the target locations by users.

- The communication/synchronization subsystem can furnish the facility of resource protection by exploiting conventional memory management schemes.

- 4. A high-speed remote-data cache mechanism can be implemented accompanied with the MBCS scheme, because a direct manipulation on cache-memory locations is suitable for cache subsystems.

From the viewpoint of the MBCS scheme, the MBP is a fine-grained hardware implementation, and the MBCF is a medium-grained software implementation. Owing to its purely software implementation, the

MBCF is able to use commodity network hardware (e.g., ethernet cards and cabling). In spite of this use of commodity network items alone, recent generations of high-performance processors have been able to attain very good performances in communications and synchronization according to the MBCS scheme. The big problem with the MBP approach is that the fine-grained communications induced by the MBP are inefficient in transmission on the buses of a node or over a network. Since off-the-shelf medium-grained network hardware is controlled by software in the MBCF, the grain-size used in communications can be enlarged to reduce overheads and to more efficiently utilize the network or buses.

Since the MBP was originally invented as a advanced hardware DSM mechanism, it naturally provided users remote-cache capability. The MBCF, however, isn't a representation of any DSM schemes but a software implementation of the MBCS scheme. In order to construct efficient remote-cache facility with the MBCF, a brand-new approach on software DSM was required. The new approach is a compiler-assisted DSM schemes which is briefly mentioned above subsection on software DSM and is described in Chapter 7.

Recently I have developed another hardware implementation of the MBCS scheme. We call it the Memory-Based Processor II (MBP2). The architecture of the MBP2 is improved by adopting the MBCF approach. The MBP2 is a medium-grained hardware implementation of the MBCS using commodity network items. The MBP2 can relieve main processors of a large part of their loads on communications and synchronization.

#### 1.4 Contributions

The main contributions of this work are listed below.

- 1. Memory-Based Processor (MBP)

- An address translation system for remote memory accesses

The MBP system was the first to introduce an address-translation system for protected memory-based communications.

- The hierarchical multicasting and acknowledge-message combining method

This method of the MBP system resolves the hot-spot problem in the collection of acknowledge-messages at a home node. This method is a key technology for the construction of large-scale coherent DSM systems.

- 2. Memory-Based Communication Facility (MBCF)

- The MBCF method

Various functions that exploit information on target locations have been proposed in the MBCF scheme, and various implementation techniques, in terms of both software engineering and advanced processor architectures, were introduced to develop the protocol stack for the MBCF.

#### • Proof of the qualitative superiority of the MBCF

The MBCF is qualitatively superior to message-passing-type interfaces and to the SparcStation Active Message. In other words, the MBCF-style interface is fit for higher-speed implementation than the other interfaces.

#### • Design of the MBCF/Ether protocol

A protocol to provide the MBCF over ethernet connections was designed. This new packet protocol was necessary to guarantee the arrival and order of packets. A new window-based (GO-back-N) technique, in which N is dynamically decreased at a hint of a lack of buffers, was also adopted for the protocol. The technique ensures that the system is both high performance and scalable.

#### • Implementation of MBCF/Ether-based system

The MBCF/Ether was actually implemented and refined on clusters of workstations, in this case SPARCstation 20s and Ultra 60s, with the SSS-CORE operating system.

#### • Experimental verification of MBCF/Ether's performance

Clusters of workstations with 100BASE-TX or 1000BASE-SX were used to evaluate the MBCF/Ether system's performance. The results were a one-way latency of in  $24.5\mu$ sec and data-transfer rate of 11.93Mbyte/sec for 100BASE-TX and a one-way latency of  $9.6\mu$ sec and data-transfer rate of 80.92Mbyte/sec for 1000BASE-SX. Note that communications during the measurements were between two user-level tasks and the processing times and round-trip times were measured from within a user-level task.

#### 3. The compiler-assisted software DSM approach

A brand-new approach to the software DSM is proposed in this thesis. In this approach, user-level codes for consistency management are inserted in the program code at compile time, and thus included in the executable modules, and both the original code and the inserted coded are thoroughly optimized to reduce overheads and the need for remote communications. This approach is revolutionary and abandons the trap-based method of conventional software DSMs. This approach allows workstations with off-the-shelf network-interface cards (e.g., 100BASE-TX ethernet) to efficiently support shared-memory parallel programs.

## 1.5 Thesis organization

The Memory-Based Processor (MBP), my first hardware implementation of the Memory-Based Communication and Synchronization (MBCS) scheme, is described in Chapter 2. Chapter 3 introduces the Memory-Based Communication Facility (MBCF), a software implementation of the MBCS scheme which requires only commodity machines (personal-computers and workstations). Chapter 3 mentions some important concepts of the MBCF, including the differences between the MBCF and the MBP, protection and security mechanism, and its virtual and global addressing system. Chapter 3 also illustrates behavior of several MBCF commands to convey a more detailed understanding of the MBCF. Chapter 4 presents variations of the MBCF functions. The wide variety of the MBCF functions is a strong point of the MBCF scheme. Chapter 5 discusses the high-speed implementation techniques and qualitative aspects of the MBCF. There are reasons why the MBCF scheme is superior to the message-passing-type communication interfaces and the Active Message scheme. Chapter 6 describes specifications of the MBCF/Ether which is an implementation of the MBCF scheme to ethernet systems. Chapter 6 also shows performance evaluations of the MBCF/Ether. Chapter 7 describes compiler-assisted distributed shared memory schemes for the medium-grained MBCS. I proposes two brand-new DSM schemes: UDSM and ADSM which are supported by our optimizing compiler: RCOP. Chapter 8 presents Memory-Based Processor II (MBP2) which is a medium-grained hardware implementation of the MBCS. In this chapter I introduce a new architecture of the MBP2 and discuss its advantages and disadvantages. Chapter 9 concludes the thesis.

# **Chapter 2**

# **Memory-Based Processor (MBP)**

## 2.1 Fine-grained hardware implementation of the MBCS

The Memory-Based Processor (MBP) [41, 34, 45, 44] is first hardware mechanism for the Memory-Based Communications and Synchronization (MBCS) scheme. The MBP is a kind of co-processor for conventional high-end microprocessor and it is attached in memory modules. It realize remote memory operations (including atomic operations), memory-based synchronization, and memory consistency protocols. Since the system with MBPs was originally designed as an advanced implementation of hardware DSM system, the size of data which an MBP handles at a time is equal to the size of data which the main-processor accesses. Consequently the grain-size is the cache-block size of the main-processor. Though this size is too fine to mitigate the overhead cost for communications, there is no other way to keep characteristics of hardware DSMs.

The MBP was designed not only as a building-block of a hardware DSM system but also as a MBCS mechanism in which communications and synchronization are handled as kinds of logical memory operations. I represent outline of the MBP system and key technology of the MBP in this chapter. The MBP's functions on communications and synchronization are almost same as the MBCF's functions which is described in Chapter 4, the differences of two parties only are on grain sizes. The MBP has multiple consistency protocols [44] to construct the hardware DSM space, and they can be mixed to use without inconsistency. These consistency protocols are not described in this thesis because they are irrelevant to the MBCS scheme.

## 2.2 Outline of the Memory-Based Processor

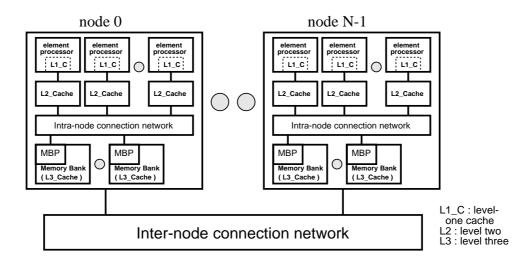

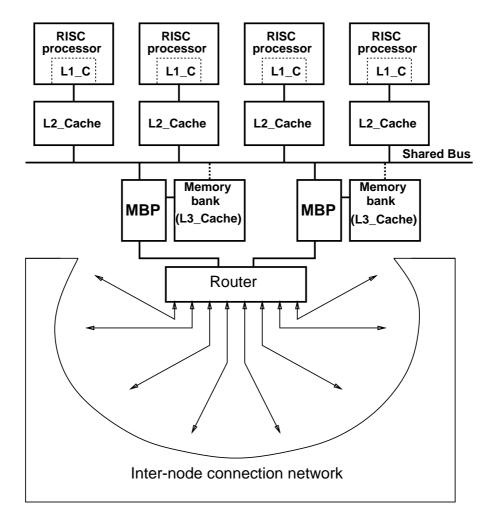

The MBP is a novel device for the realization of protected and virtualized high-speed user-level communications and synchronization in NUMA systems. Figure 2.1 shows the architecture of a system in which

Figure 2.1: System architecture using MBPs

MBPs are used and Figure 2.2 illustrates the structure of a node of the system. In this system, each set of strongly-cooperative threads with fine-grained concurrency would be allocated to a single node, while tasks might be scheduled at more than one node for a more coarsely-grained parallelism. The MBP is attached to each memory bank on the lowest level of the memory hierarchy and it performs activities in which there are no useful localities on memory references for main processors to improve performance. Therefore, the system is equipped with multiple MBPs that can access the memory-modules quickly and directly. As you see from Figure 2.1 and Figure 2.2, the MBP architecture is a pioneering processor-in-memory (PIM) architecture. Using RISC processors as the main processing elements of the system provides the best performance in computation with access-locality on memory references. This is because the RISC processors integrate large amount of resources (registers and cache memory) which exploit access-locality to improve performance. For short-threaded fine-grained computation without access-locality the characteristics of the MBP complement those of RISC processors [41].

The MBP receives command messages that originate from the main processing elements (conventional RISC microprocessors) as main-memory operations (i.e. outgoing load/store operations). MBPs are responsible for data transmission among the memory banks, management of the consistency of the caching system, various memory-based synchronization mechanisms [34], page management of virtual shared memory, the management of context in the main processing elements, and so on. In this context, MBPs work to maintain memory consistency among nodes and to execute inter-node communications.

The MBPs in a system make up a high-performance/high-functional distributed shared memory space for a NUMA system [34, 44]. In a system with MBPs, memory-management units (including TLB mechanisms)

Figure 2.2: Structure in one node of the MBP system

are extended to support facilities for remote-memory access, and the system provides users with the same finegrained memory interface as an SMP. The MBPs also support fine-grain cache-consistency protocols of both the invalidation types and the update types, and include various memory-based synchronization primitives.

## 2.3 Caching in the MBP system

The memory banks are used as caches of the data from remote nodes that is required by inter-node memory references and as main memory for local data. The system thus has hierarchical cache system: the on-chip caches of the processors (L1 caches) are at level 1, 'snoop caches' (L2 caches) are at level 2 and the memory banks of the nodes are at level 3. Page-level directory schemes such as IVY[32] were used in the MBP systems instead of cache-block-level directory schemes [31], in order to reduce the amount of directory memory and to use translation look-aside buffers (TLBs) to accelerate consistency-preserving operations. The unit of data transmission, however, is the size of an L1 cache block instead of that of a memory-page corresponding to a TLB entry. This is to reduce the amount of wasteful data traffic that arises in the case where the unit of transmission is the page. Each block in memory banks has state tags that are used to maintain consistency and reduce the amount of bus traffic in each node. A **pseudo-fullmap** [34, 44] method was adopted for the inter-node directory scheme. This method assumes that the inter-node network has a hierarchical structure and reduces not only the cost (in terms of time) of maintaining cache consistency but also the amount of space taken up by directory entries. I will describe this directory scheme later.

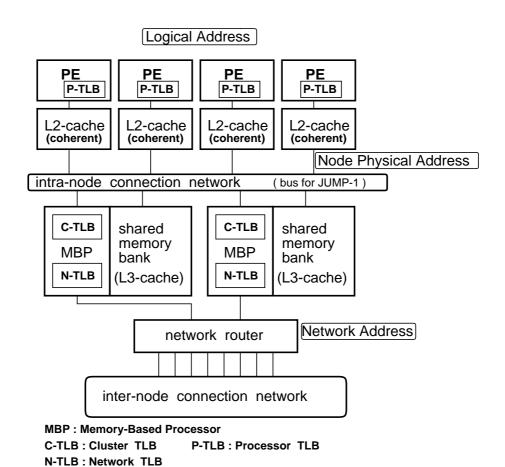

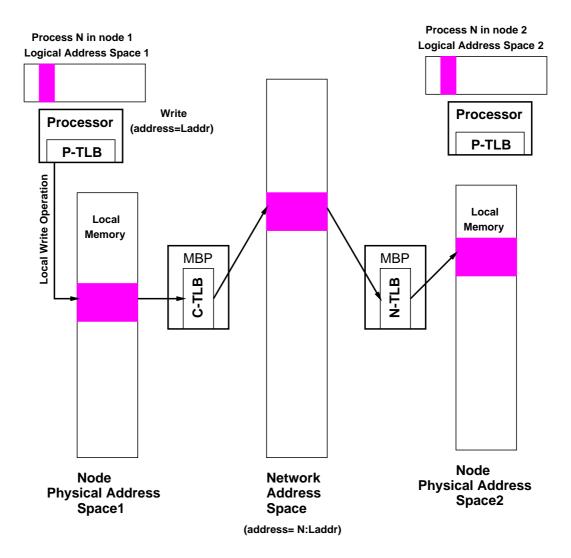

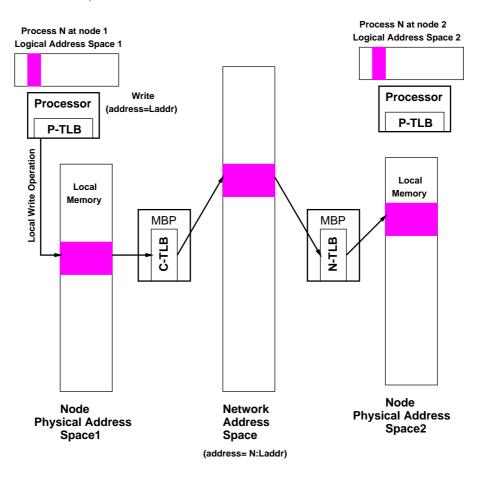

## 2.4 Address translation in the MBP system

Fully virtual shared memory is implemented with a two-stage address translation scheme. In a clustered system, there are three classifications for address spaces. The first is the logical space in a main processing element, and this is called a 'logical address' space. The second is the physical address space of a node, and is called a 'node-physical address' space. The third is the network-wide logical space, and is called a 'network address' space. The network address space is the unique virtual shared-memory space of the system.

Memory protection for the global network address space is much the same as in the conventional MMU/TLB system. In other words, page-fault traps are used to detect access violations by processing elements.

The TLB in a main processing element is used for the high-speed translation of logical addresses to node physical addresses. A cluster-translation look-aside buffer (**C-TLB**) and a network translation look-aside buffer (**N-TLB**) have been implemented in the MBP to accelerate translation of addresses and management

Figure 2.3: TLBs in one node of the MBP system

Figure 2.4: Address translation in the MBP system

of consistency (refer to Figure 2.3). The C-TLB translates the node-physical address in a cluster to a network address and has a room in its entry for caching the associated directory of the L3 cache system, and thus raising the system's performance. C-TLBs always monitor the bus transactions in a node and check operations in terms of requirements for inter-node consistency. If it is needed, the MBP is invoked as needed to maintain consistency. The N-TLB checks messages from external nodes, translates network addresses to node-physical addresses, and invokes the MBP for processing of operations at the target node-physical address. Each time a location in memory is modified or fetched by external nodes, the state tags of the target node-physical address are checked. Bus transactions are then performed as required to maintain consistency in the node.

My two-stage address-translation scheme enables update-type protocols and makes the use of main memory for L3 caching feasible (refer to Figure 2.4). This is why it is possible to use the different node-physical addresses in the respective nodes for one shared memory location (one network address) and thus to have translation between network addresses and physical addresses take place locally. The MBP is the earliest mechanism to have a two-stage address-translation scheme that is extended to cover remote-memory access.

### 2.5 Directory-based cache scheme in the MBP system

The MBP also introduces two brand-new techniques on directory-based cache schemes. One is the "hierarchical bitmap directory" which reduces the amount of memory required to store directory entries, and another is the "hierarchical multicasting and acknowledge-message combining" which resolves bottlenecks that arise in the transmitting of multicasting-packets and processing of acknowledge-packets at source nodes.

The directory system, the MBP's "pseudo-fullmap directory", has three type formats which can be selected according to the situations of individual applications. The hierarchical bitmap is one of the three types and is suitable for large-scale shared-memory systems.

My directory scheme exploits the hierarchical structure of the system and the hardware routing technology, and is therefore based on two assumptions. One is that tree-type network can be efficiently emulated on the interconnection network of the system. The other is that the system has intelligent hardware routers which can support the "hierarchical multicasting and acknowledge-message combining" method.

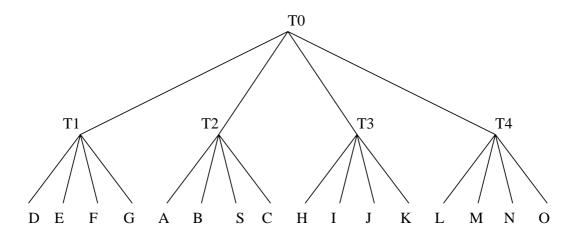

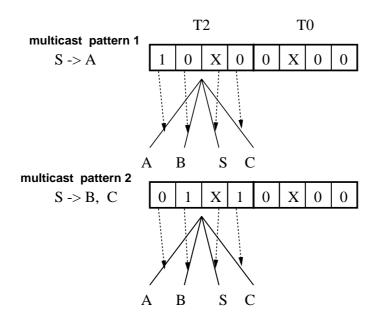

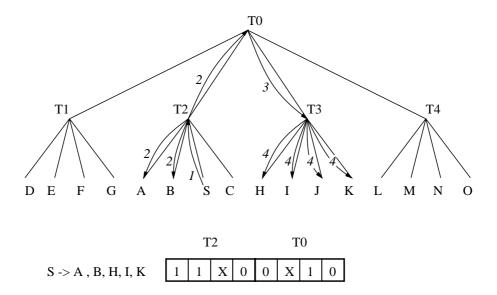

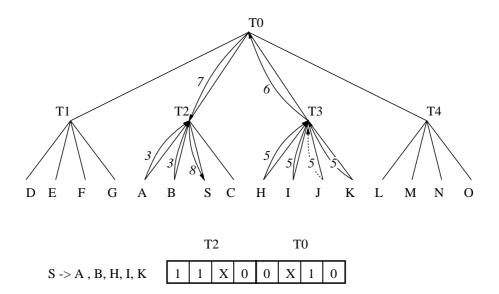

The basic idea of the hierarchical bitmap directory is explained with the aid of Figure 2.5 and Figure 2.6. We assume that there is a quad-tree-type inter-node connection network in the system. Figure 2.5 shows a network with 16 nodes and the patterns of directory bitmaps at the node "S". In this figure, an alphabetical character represents a node of the system and the node indicated by "S" is the node I will focus in describing the bitmap patterns. The quad-tree network has a two-layered structure and five routing points. The highest-

Figure 2.5: Hierarchical bitmap directory (1)

Figure 2.6: Hierarchical bitmap directory (2)

0 0

$S \rightarrow A$ , B, H, I, J, K

0

level routing point is the global root "T0" and I name the other 4 points as "T1", "T2", "T3", and "T4" respectively. There are two routing points: "T2" and "T0" between the node "S" and the global root. The hierarchical bitmap at the node "S" consists of the bitmap that indicates selections at "T2" and the bitmap that indicates selections at "T0". Each bit of the bitmap for "T2" or "T0" corresponds to a link (branch) of a subtree of the network. A "1" in the bitmap means that child node(s) of the corresponding link is enrolled in the map. Figure 2.5 shows two bitmap patterns which represent simple cases in which each selected links lead to only single nodes. Note that the "X" bit corresponds to links which are routes to the global root from the node "S" and the values in these bits are irrelevant to the hierarchical bitmap scheme, and thus these bits can be omitted in actual implementations. Figure 2.6 shows a bitmap pattern which includes a selected link corresponding to multiple nodes. In this figure the third link of "T0" is activated and this means that the map includes 4 nodes: "H", "I", "J", and "K". The bitmap does not indicate which of these 4 nodes are really intended for inclusion in the map. This lack of information enables us to reduce memory sizes required for directories. I allow unnecessary communications because of lack of information in the hierarchical bitmap scheme, and each node dynamically decides whether a reaction is really required of the system as each packet is received. The actual decisions are based on whether or not there are cached copies of some relevant data at the respective nodes.

Figure 2.7: Hierarchical multicasting

Figure 2.7 illustrates the action of hierarchical multicasting using the hierarchical bitmap directory. An update-message or an invalidate-message is transmitted from the node "S" to the nodes "A", "B", "H", "I", and "K", all of which have cached copies of data from "S". The numerical characters in the figure represent the order of actions.

- 1. A message-packet from "S" reaches the routing point "T2".

- 2. The router at "T2" multicasts the packets to three directions: to the node "A", to the node "B" and to the parent routing point "T0". Two of these directions (to "A" and to "B") correspond to the bitmap for "T2". The uplink of the packet to "T0" is required because of the non-zero bitmap for "T0".

- 3. The router at "T0" multicasts the packet in only one direction (to "T3"), in which lies the nodes "H", "I", "J", and "K". This direction corresponds to the "1" in the third bit of the bitmap for "T0".

- 4. The router at "T3" multicasts the packet in all directions (i.e. it broadcasts the packet). The hierarchical bitmap does not contain information for selecting directions at "T3".

After these actions 6 nodes "A", "B", "H", "T", "J", and "K" have received packets from "S". The packet received at the node "J" is unnecessary and is ignored because there is no cached copy of the data to be updated at this node. The large-scale multicasting mechanism can thus be efficiently implemented using the hierarchical multicasting.

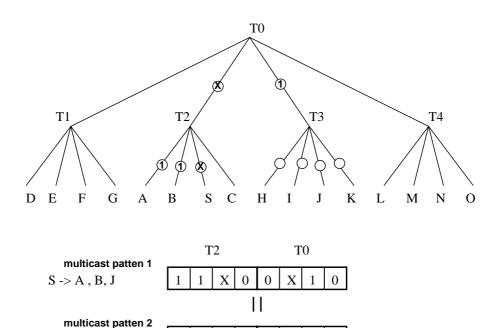

Figure 2.8: Acknowledge-message combining

Figure 2.8 illustrates action of an "acknowledge-message combining" operation. The "acknowledge-message combining" method complements the "hierarchical multicasting" method, and it is used for the acknowledge-reply phase of operation in response to a multicast-message. In the figure I assume the same situation as in Figure 2.7. The numerals in Figure 2.8 represent the order of actions and in sequence from the numerals in Figure 2.7.

- 1. "A" and "B" reply acknowledge-messages to the routing point "T2".

- 2. No action. The router at "T2" waits for the arrival of the acknowledge-message from the parent nodes direction.

- 3. 4 nodes "H", "T", "J", and "K" reply acknowledge-messages to the routing point "T3". More accurately, "J" replies with a dummy acknowledge-message, as no action is taken at that node.

- 4. The router at "T3" has now received acknowledge-messages from all of its child-node directions. It then combines the four messages, and sends this acknowledge-message in the direction of its parent node.

- 5. The router at "T0" has received the single acknowledge-message that corresponds to the single message sent from "T0", and replies with an acknowledge-message to "T2".

- 6. The router at "T2" has finally received the acknowledge-message from "T0", and it now combines the

three messages (from "A", "B", and "T0"), and replies, with a single acknowledge-message, to the requesting node "S".

The node "S" only receives a single message to acknowledge the successful multicasting of the original invalidate-message or update-message to multiple target nodes. The "acknowledge-message combining" technique can thus dramatically reduce overheads in terms of the processing of acknowledge-messages at a requesting node.

### 2.6 The MBP's protocol-switching facility

There are several consistency protocols in the MBP system: invalidate-type protocols, update-type protocols and non-cacheable remote-memory operations. They can be dynamically switched at any time without carrying inconsistencies. Using these protocols, an MBP switches between consistency management strategies for directory-based L3-caches on the basis of the attributes that specify data-access types and are attached to each entry of the TLB and/or the C-TLB [45]. Maintaining perfect inter-node consistency for all access patterns is a costly operation and dedicated protocols for maintaining limited access patterns are feasible under the protocol-switching mechanism. Therefore, to improve system performance, I have defined and use new protocols which do not generally produce consistency but are consistent with some restrictions on application code [34]. The variant protocols in the MBP clustered system are illustrated in the reference [44].

#### 2.7 Related Works

#### 2.7.1 Memory Channel (Reflective-Memory)

The Memory Channel [14] is a hardware mechanism for fine-grained communications and is based on the Encore's Reflective-Memory Multiprocessor [12, 33]. DEC's sever machines adopted this mechanism for inter-node communications. This mechanism is very similar to the basic mechanism of the first MBP. In particular, the address-translation scheme and message-invocation scheme are identical. The MBP was, however, earlier than either the Memory Channel or Reflective-Memory. Moreover, the MBP is greatly superior to these mechanisms, because the Memory Channel or Reflective-Memory has neither an efficient scheme for collecting acknowledge-messages to match the acknowledge-message combining of the MBP nor any invalidate-type protocols to maintain consistency.

### **2.7.2** Tempest

The Tempest [63] is a hardware mechanism for detecting access by processors to actual shared blocks in a shared memory space. A similar mechanism is included in the MBP, and the MBP was both designed and reported on in published work much earlier than was the Tempest. The difference between the Tempest and the MBP is the mechanism for sending messages. The Tempest generates interrupts to the main processors when some communications is needed to maintain consistency, and the main processors send the required messages from the corresponding interrupt routines. The MBP performs fine-grained communications by using a dedicated hard-wired circuit. The Tempest detects fine-grained access by the main processors, so interrupts occur too frequently to allow an improved performance for the system as a whole.

#### 2.7.3 Flash

The Flash [29] is the successor to the DASH [31, 30] multiprocessor and includes an integrated protocol processor which detects fine-grained access by the main processors to shared blocks and handles the communications required to maintain consistency. Its basic functions are thus similar to those of the MBP, but the Flash has no virtual network-address space and is not able to exploit the main memory as a level-3 cache. The Flash only has an invalidate-type shared-memory protocol, so calculations and communications cannot be allowed to overlap in its shared-memory scheme. The Flash has a facility, therefore, for message-passing-type communications. With the MBP or the MBCF, however, this problem was successfully overcome by using update-type protocols or remote-writes within the frame work of the shared-memory.

#### **2.7.4** Shrimp

The Shrimp [4] is for the hardware support of fine-grained update-type shared-memory traffic, such as that which occurs in Reflective-Memory (i.e., the Memory Channel). The Shrimp is very simple hardware and can only generate and transfer one remote packet on each shared-access of main processors. The Shrimp mechanism is thus a subset of the Memory Channel and so in turn is a subset of a subset of the MBP. The Shrimp is the latest of these devices but has the lowest level of functionality. The Shrimp is not an interesting device in comparison with the others, but the team which developed the Shrimp developed some interesting shared-memory protocols (e.g., AURC [22]) which can be applied to the Shrimp or to compiler-based DSM schemes.

# **Chapter 3**

# Overview of Memory-Based Communication Facility (MBCF)

## 3.1 Middle-grained software implementation of the MBCS

The Memory-Based Communication Facility (MBCF)[46, 52, 47] is second implementation of the Memory-Based Communications and Synchronization (MBCS) scheme and first software one of the MBCS. Since conventional off-the-shelf network interface cards (NIC) are exploited in the MBCF system, grain size of communications is larger than that in the MBP system. The size of data which the MBCF system handles at a time is equal to the size of data-packet which the NIC transfers. Consequently the MBCF is a medium-grained (or coarse-grained) software implementation of the MBCS. Though this grain-size is suitable for mitigation of the overhead cost for communications, it is too large to realize a remote-cache subsystem. Therefore I needed to invent a brand-new software DSM approach for the MBCF. This new software DSM approach will be shown in Chapter 7.

In this chapter I will describe basic concepts and basic mechanisms on the MBCF. Next I will represent a wide variety of the MBCF functions in Chapter 4, and give discussions on qualitative points of the MBCF in Chapter 5. In Chapter 6 I will explain a concrete implementation of the MBCF using ethernet and give the result of its performance evaluations.

# 3.2 Background to the MBCF

The MBCF is a software-only solution for the realization of protected and virtualized high-speed user-level communications and synchronization. The MBCF was invented as part of Network of Workstations (NOW) project and is for distributed-memory multiprocessor systems that do not have hardware DSM mechanisms.

So far, many hardware DSM mechanisms (including MBP) are proposed and no DSM mechanism has been proved to be sufficiently cost-effective and general for wide range of applications. The WSs/PCs of recent times are very powerful but, because of mass-productions, they are inexpensive. The performance of their network interfaces has also improved rapidly. They can therefore be used as the nodes of parallel computers. Hardware for LAN communications is usually available for such machines, and the performance of such hardware is also subject to rapid and continued improvement. Hardware DSM mechanisms are not able to exploit LAN hardware and require additional special hardware for communications. This represents a double investment in communication functions and makes the systems expensive. Another big drawback of hardware DSM mechanisms is that their granularity of communications is too fine to bring out the maximum performance of either network hardware or DMA hardware. The granularity of communications is comparable to the amount of data accessible in a single processor operation, and is less than or equal to the size of a cache line. Since, for microprocessors of recent generations, the outgoing memory-access operation which is required to invoke some function of the hardware DSM mechanism for a transmission is more expensive than the software processing of hundreds of instructions within the on-chip cache, a hardware DSM mechanism that is based on fine-grained transmission will be poor at high-bandwidth applications. Therefore, if we assume that our system has fast communication hardware for LAN (e.g., gigabit ethernet) with a bandwidth that is comparable to that of a hardware DSM mechanism, it is probably true that applying light-weight softwarebased protocols to the communication hardware will provide a performance that surpasses that of hardware DSM mechanisms in terms of maximum throughput. We consequently need to develop efficient methods for user-level communications and synchronization that only require commodity-hardware mechanisms.

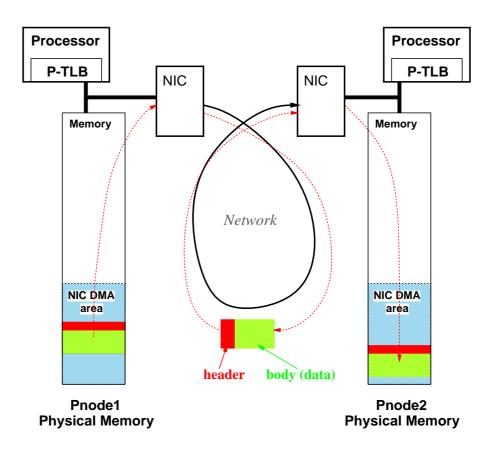

I assume that the MBCF system is equipped with off-the-shelf network interface cards: NICs (e.g., ethernet cards). These cards have no functionality for protection or security, transmitting memory images as packets to other nodes, or receiving packets from other nodes into a specified ring buffer in the system (kernel) space.

Two factors produce most of the overheads resulting from user-level communications and synchronization. The first is the methodological factor (i.e., functionalities, protocols, packet formats, etc.). Conventional user-level communication interfaces (for examples, TCP/IP [62], UDP/IP [61] and MPI [17]) are of the message-passing type, and their functions are limited, in remote-write operations, to specific message-buffer addresses of the kernel-space. To break out of this limitation, I adopted a memory-based form of operation, in which arbitrary target addresses and a wide variety of functions are available. By using memory-based operations, protection and virtualization in communications and synchronization can be replaced with those in memory access operations that are induced by original memory-based communications and synchronization.

This replacement makes high-speed implementation of the scheme feasible, since the advanced architectural mechanisms of processors in terms of memory access can then be exploited.

The other is the software-engineering factor (implementation methodology). In a conventional OS, communications between and synchronization of nodes (machines) is regarded as a set of typical I/O events, like disk operations, and device-drivers for communications and synchronization exploit service routines in common with other I/O devices. Consequently, the device-drivers suffer rather large processing overheads that are superfluous in terms of the functions of communications and synchronization. To realize a high-performance implementation, MBCF-dedicated system-calls and MBCF-dedicated interrupt routines have been developed and used, so that no operations are irrelevant to the functions of the MBCF. The MBCF thus implemented is free of the problems arising from the second factor (the software-engineering factor).

### 3.3 Basic concepts of the MBCF

#### 3.3.1 From MBP to MBCF

The MBCF uses pure software routines to emulate the MBP's functions. The three types of software mechanisms are user-level-request codes (packet-sending codes), MBCF-dedicated interrupt handlers and MBCF-dedicated system-calls. In the MBP system, a remote memory access is invoked by a processor's operation on memory. When an MBP detects access, by a processor, to memory at a target address that belongs to a remote node (the target node), the MBP translates the access information into a format for inter-node communications, and makes a packet, then transmits it to the target node. When the MBP in the target node receives the packet, it executes the remote-access specified in the packet and returns a reply if necessary. In the MBCF system, on the other hand, remote memory access is invoked by an explicit system-call for an MBCF function. Firstly, a user-program prepares an MBCF packet in user-mode and executes the MBCF-requesting system-call. Secondly, the kernel-level routine of the MBCF-dedicated requesting system-call makes a packet for inter-node communications and transmits it via conventional NICs. Finally, the MBCF-dedicated interrupt routine at the target node receives the packet, immediately executes the remote-access operation specified by the packet, and returns a reply if necessary. In comparison with an MBP system, an MBCF system carries some additional software overhead, but an MBCF packet need not correspond to a memory access operation by a processor. This flexibility means that the MBCF provides opportunities in terms of optimization of the number of packets and amount of data being communicated. More specifically, large amount of data can be handled in a single MBCF operation and/or multiple MBCF operations can be merged into a single packet. I call such a merged packet a "combined packet" and refer to this technique for optimization as "combining". If a system has rather poor communication hardware in comparison with its processor power, these opportunities

for optimization must be seized to obtain efficient execution.

# 3.3.2 Protection and security mechanisms of the MBCF

In the MBCF scheme, an MBCF-dedicated kernel-level interrupt routine makes the actual access to the target location of an operation requiring access to remote memory. If strong protection and security are required for the system, powerful capability-checking or authentication procedures can be added to this interrupt routine. However, such additions, of course increase the overhead of the MBCF interrupt routine. To avoid increasing the overhead in this way, I developed a novel method that exploits page-aliases and simple access-keys.

In parallel processing, when some error occurs during an activity, the further execution of related activities is probably meaningless. Owing to this characteristic a simple protection mechanism which merely separates a task from other unrelated tasks is sufficient. To prevent the spread of the bad effects of an error to other tasks, the MBCF uses logical address spaces with a memory-management mechanism. Only those memory areas which are mapped to the target task can be accessed through the MBCF. To protect memory from attacks by other tasks, I adopted a unique access-key to represent the right to access a target memory-space.

On the other hand, in distributed processing (e.g., the client-server model) the server's activities must be protected from errors during and attacks by client activities. In this case, a strict protection mechanism which distinguishes the working area on each client from the working areas on the server and the other clients is required. I solved this issue by using a combination of unique access-key and page-aliasing. In Section 3.4, I will include this protection scheme in an illustration of the behavior of the MBCF, so I only describe the scheme in outline from here.

When the server requests MBCF communications with a distrusted client, the server creates an agent (an activity with its own independent memory-space) within the server's node, and delegates the job of communicating with the client to the agent. The server then allocates a working-memory area for use in communication with the client, and this area is also mapped to the agent. In other words, the area is intranode shared-memory shared between the server and the agent by using a page-alias mechanism. After these preparations on the server's node, the agent informs the client of the agent's access-key (but not the server's access-key), and the client uses the agent's memory-space to communicate with the server. Even if the client has an evil intention, such as to destroy the server, it can only damage the agent's space and can NOT stop the execution of other server activities.

In both the MBCF scheme and MBP schemes, protection and virtualization in communications and synchronization are replaced with protection and virtualization of memory accesses. This replacement makes a high-speed implementation of the mechanisms involved feasible. Especially in the MBCF scheme, since

the TLBs and the MMUs of node processors (conventional microprocessors) are exploited for the translation of actual accesses in target nodes, no additional hardware mechanisms are required to improve performance.

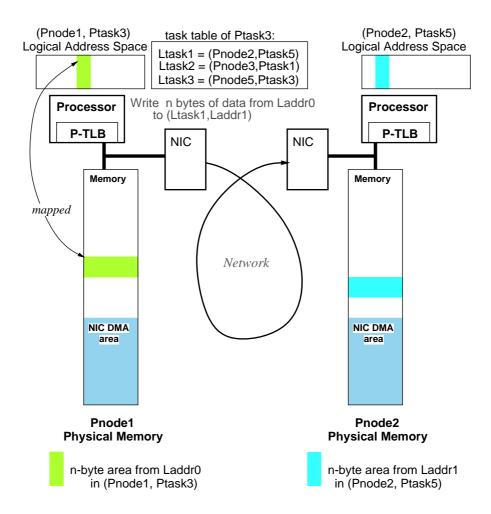

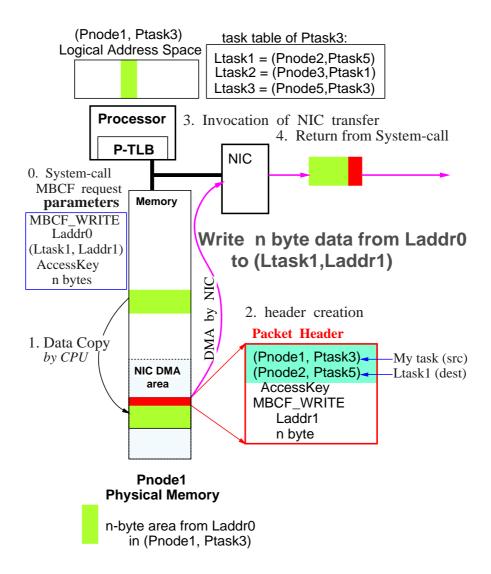

# 3.3.3 Virtual and global addressing in the MBCF system